판교 전역 팹리스에 시스템반도체 설계SW 무료 제공

정부는 8일 국내에서 팹리스(반도체 설계 전문기업)가 가장 많이 밀집한 판교 전역에 고가의 시스템반도체 설계 소프트웨어인 전자설계자동화(EDA) 툴을 무료로 제공한다고 밝혔다.

정부는 이날 정부서울청사에서 열린 ‘제2차 혁신성장 빅3 추진회의’를 열고 ‘팹리스 성장 인프라 조성 방안’을 발표했다.

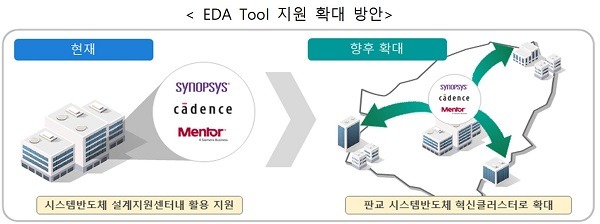

이에 따르면 먼저 EDA 툴 지원 대상이 기존 설계지원센터 입주 기업에서 판교 전역의 초기 팹리스로 확대된다.

현재 판교에서 활동 중인 국내 팹리스 비중은 약 70~80%(한국반도체산업협회 회원사 기준)에 달한다.

또한 팹리스가 AI 반도체 설계 뿐만 아니라 설계한 반도체 성능을 검증·최적화할 수 있도록 EDA Tool의 종류·개수도 확대한다. 2021년까지는 27종 70개, 2022년앤 42종 151개로 확대될 예정이다.

아울러 EDA Tool 활용에 어려움을 겪는 초기 팹리스를 대상으로 전문교육도 추진한다.

반도체IP(반도체설계자산)와 관련해선 단기적으로는 글로벌 핵심IP를 국내 팹리스가 자유롭게 활용할 수 있도록 지원하고, 중장기적으로 핵심IP에 대한 국내 역량을 제고한다.

고가의 글로벌 IP를 국내 팹리스가 무료 또는 저렴한 가격으로 사용할 수 있는 지원 프로그램을 마련, 완제품 설계 전까지 IP 무료 이용, IP 특가 제공 등 글로벌 협업을 통한 지원을 강화한다.

또한 국내에서 개발된 반도체IP의 데이터베이스(IP뱅크)를 구축하고 반도체산업협회, 전자기술연구원 등이 국내 IP를 재설계·사업화한다.

이는 시스템반도체 설계지원센터를 통해 2021년 상반기 시범사업으로 추진될 예정이다.

설계패키지 지원 규모도 13개 기업에서 18개 기업으로 확대하고 반도체IP 대표기업 Pool을 구성, 참여 기업과 중기부간 업무협약 체결 후 팹리스 지원를 지원한다.

이와 함께 IoT, AI, 자율차 등의 핵심IP를 자립화해 해외로 빠져나가는 반도체IP 라이선스 비용을 최소화하고 국내IP 개발로 파운드리 보유 IP 확대 및 팹리스-파운드리의 연대·협력을 도모한다.

인공지능 학습·추론 등에 필요한 고성능 AI 반도체용 IP 기술개발도 지원하고 미세공정에 맞게 기 개발된 IP 최적화·보완 등 팹리스의 사업화 기술애로로 지원한다.

정부는 팹리스의 파운드리(위탁 생산) 부족 상황에 대응하기 위해 단기적으로 시제품 제작용 멀티프로젝트웨이퍼(MPW) 이용 부담을 완화하기로 했다.

MPW 지원액은 연간 15억원에서 25억원으로 확대된다. 1건당 지원액은 약 1억원 정도다. 앞으로 지원 체계도 일반공정(28㎚~180㎚)과 미세공정(28㎚ 이하)로 구분해 세분화될 예정이다.

아울러 협회를 중심으로 파운드리 성장 협의체를 구성, 디지털·아날로그 등의 공정개방을 지속협의하고 애로해소를 추진할 방침이다.

신규 파운드리 증설을 위한 프로젝트 발굴에도 나서 4차 산업혁명, 비대면 경제 등으로 초과 수요 상태인 국내 파운드리의 기존 설비투자 지원 및 투자 수요 발굴을 추진한다.

기업의 투자 의향 확정시 원활한 투자 지원을 위해 인센티브 방안을 검토하고 뉴딜펀드, 정책금융 등을 활용한 투자 지원, 공동 R&D 지원 등를 검토한다.

정부는 또한 설계 SW 지원 등을 위해 기존 시스템반도체 설계지원센터 역할을 강화하고, 제2캠퍼스로 ‘인공지능 반도체 혁신설계센터’를 조성할 계획이다.

이 혁신설계센터는 제2판교에 구축 중인 글로벌 비즈센터 내에 들어설 것으로 보인다.

<Copyright © US BUSINESS NEWS TV, Unauthorized reproduction and redistribution prohibited>

Dennis Han 기자 다른기사보기